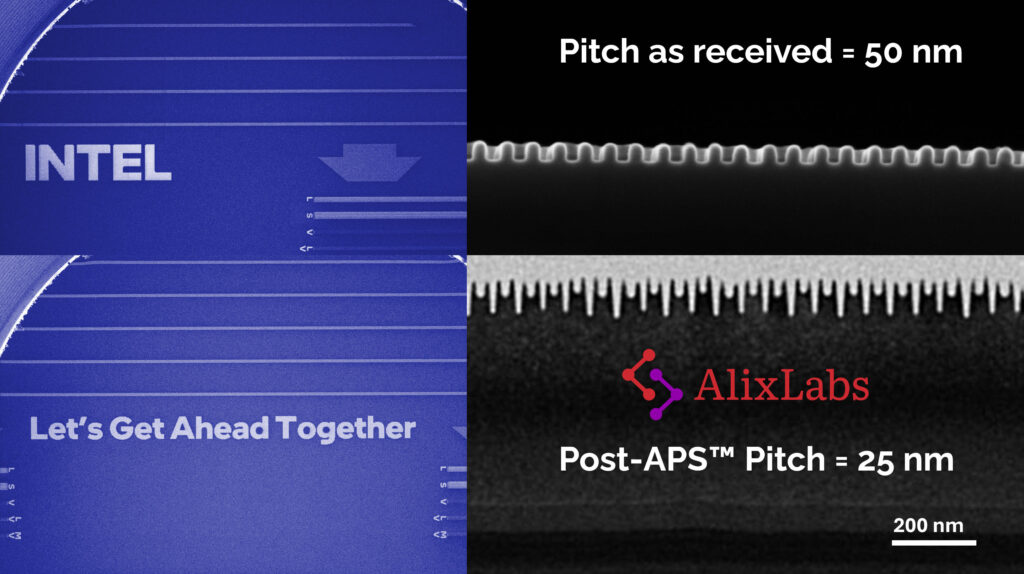

Det svenska halvledarföretaget AlixLabs meddelar att de använt sin teknik för att etsa strukturer som motsvarar kommersiella 3-nanometerskretsar på testkisel från Intel. Anmärkningsvärt är att detta gjorts utan användning av extreme ultraviolet-litografi (EUV) eller för den delen avancerad multi-patterning enligt recepten SADP och SAQP (Self-aligned double patterning respektive quad patterning).

AlixLabs är en startup baserad i Lund, som satsar på utvecklingen av Atomic Layer Etching (ALE), en typ av plasmabaserad torretsning för strukturer i spjutspetsen, och ALE Pitch Splitting, där transistorfenor klyvs med etsning. Fördelen med detta är att processen är betydligt mindre kostsam i spjutspetsen, där priserna per kiselskiva (eng. wafer) skenar för varje ny generation.

Vi är glada över att kunna visa hur APS kan hjälpa industrin att minska sitt beroende av multi-patterning, samt minska kostnaderna och miljöpåverkan. Med vår teknik har vi gjort det möjligt att producera strukturer mindre än 10-nanometersklassade på kisel, och med hjälp av Intels Test Vehicle Program har vi bevisat att strukturer mindre än 5-nanometersklassade med enbart etsning är möjligt på kisel.

Dmitry Suyatin, CTO och medgrundare av AlixLabs

Bolagets teknikchef, Dmitry Suyatin, berättar att deras demonstration möjliggjorts med hjälp av Intels Test Vehicle Program, som tillhandahållit testkisel för AlixLabs att processa med sin APS-teknik. Där ALE tidigare varit begränsat till strukturer i 10-nanometersklassen är det med AlixLabs teknik APS som kraftigt förenklat tillverkning av strukturer mindre än 5-nanometersklassen.

Att etsa 3-nanometersklassade strukturer utan avancerad EUV med endast immersionslitografi får ses som ett stort steg, förutsatt att tekniken kan skalas upp och användas i praktiska tillämpningar. Det mål som tidigare uttalats av AlixLabs är att de vill se sin teknik användas av TSMC och Samsung för tillverkning på deras motsvarande 2-nanometersprocesser.

Sedan industrin passerat tillverkning i 28-nanometersklassen har multi-patterning krävts i allt större utsträckning för att skapa mindre strukturer tillika transistorer. Det är en litografisk teknik som går ut på att dela upp komplexa mönster till flera enklare och sedan mönstra dessa i sekvens på kiselskivan för att nå högre precision och detaljer. Detta kan med litografi göras i flera steg om två, tre och fyra (SADP, SAQP). Fler är i teorin möjligt, men anses för komplext och dyrt för att vara praktiskt användbart.

APS-tekniken visar att det inte finns något behov av komplex multi-patterning som SADP och SAQP för att tillverka kretsar om 5 nanometer och mindre. Det ökar potentialen för att använda immersionslitografi i kritiska masklager även för 3-nanometersprocesser. Dessa resultat har tagits fram med vår tidiga Alpha-utrustning, med Beta-utrustning som följer senare under 2025. Vi vill tacka Intel för att de möjliggjort denna demonstration tillhandahållit testkisel i toppklass.

Jonas Sundqvist, VD och medgrundare av AlixLabs

Medan användning av litografisk multi-patterning ofta är en nödvändighet medför den flera nackdelar. Varje extra steg kräver fler masker som strålning måste passera och dessa måste riktas mycket precist för att få till det enhetliga mönster, av det komplexa som delats upp, som eftersträvas. En mindre felriktning kan ge sämre yield och lägre prestanda, men framförallt förlänger det produktionstiden från ax till limpa markant. Det är med andra ord alltid att föredra att undvika multi-patterning om möjligt.

Det är viktigt att skilja på ”nanometerklassat” och det faktiska måttet nanometer. Det AlixLabs åstadkommit är att med torretsning nå en metal pitch, avståndet mellan metalltrådarna som kopplar samman transistorgrindarna, om 25 nanometer. Detta att jämföra med TSMC:s idag mest avancerade 3-nanometersprocess, vars metal pitch kan nå så lågt som 23 nanometer. Detta är dock i ett bästa scenario där högdensitetsbibliotek använts för vissa strukturer.

AlixLabs lyfter själva deras testkisel som en viktig milstolpe på väg mot kommersialisering och berättar att fler nyheter är att vänta senare under 2025. Mer information kommer att delges av AlixLabs VD Dmitry Suyatin under konferensen SPIE Advanced Lithography + Patterning i San Jose, Kalifornien, den 27 februari klockan 9:00–9:20 lokal tid.