Moores lag (eng. Moore’s Law) utlovar en fördubbling i transistortäthet vartannat år, något som helt sonika medför dubbelt så avancerade kretsar vartannat år. Utvecklingstakten har dock senaste decenniet stannat av och den så kallade ”lagen” gäller inte längre. Kretsutvecklare har därför tvingats göra allt större kretsar, något som i sig medför problem.

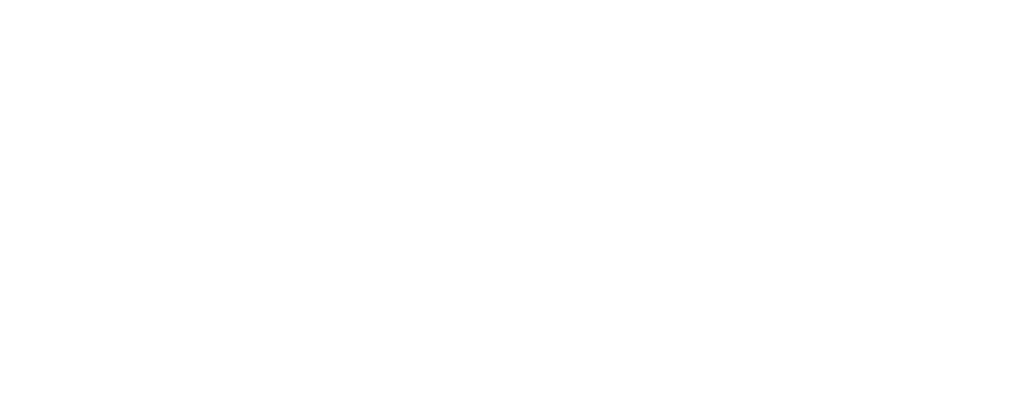

Desto större kretsarna är desto svårare är det att nå önskad yield, det vill säga antal fungerande chip vid produktion, något som tar på marginalerna. Utöver detta finns en övre gräns, reticle limit, för hur stora kretsar som kan producera med litografisk teknik. Ett sätt att lösa det ena eller båda problem är att producera flera kretsar och kombinera dessa till en färdig produkt. Dessa chiplets placeras antingen på bredden (2.5D) på ett substrat eller vertikalt (3D) ovanpå varandra.

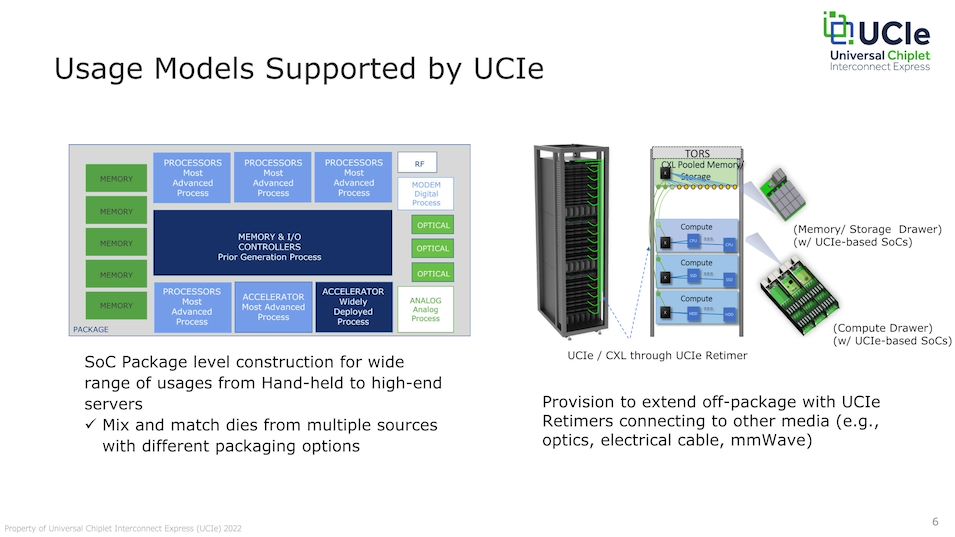

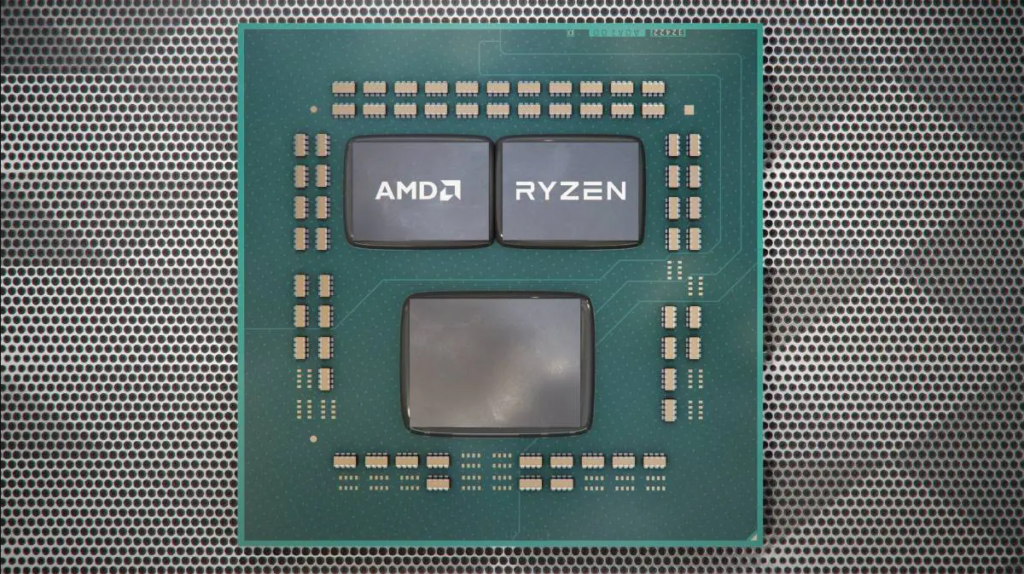

Konceptet kallas ofta chiplet, där varje enskild krets i en produktdesign är just en egen chiplet. Förutom att vara en lösning på problem möjliggör det också för att snabbare ta fram nya produkter då endast en del, en chiplet, behöver utvecklas och sedan paras ihop med redan existerande kretsar. Det sänker även kostnaden för att ta fram nya produkter. Bland annat AMD gjorde detta med Ryzen 5000-serien, där enbart den chiplet med beräkningsenheterna var ny och den chiplet med minneskontroller samt övrig I/O-funktionalitet från Ryzen 3000-serien lämnades orörd.

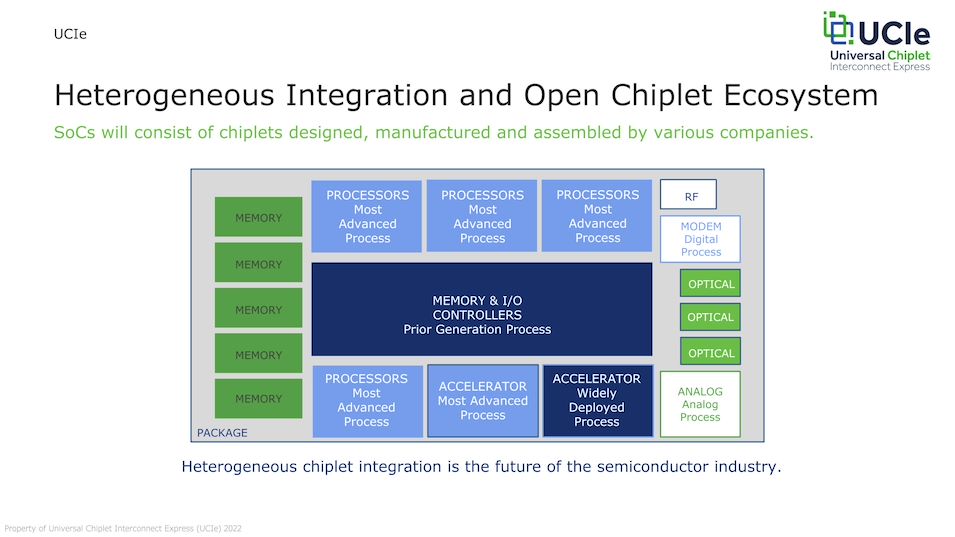

En annan fördel med chiplet-designer är möjligheten att tillverka kretsar på de noder de gör sig bäst. Där vissa delar som själva beräkningsenheterna är lättare att krympa för mer transistortäta tillverkningstekniker är andra delar svårare eller skalar rentav knappt något alls. Ett exempel på detta är minneskontrollern, som då kan tillverkas på en äldre och även billigare tillverkningsteknik.

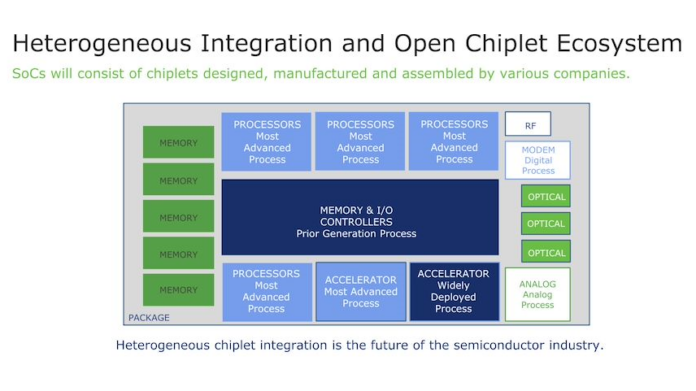

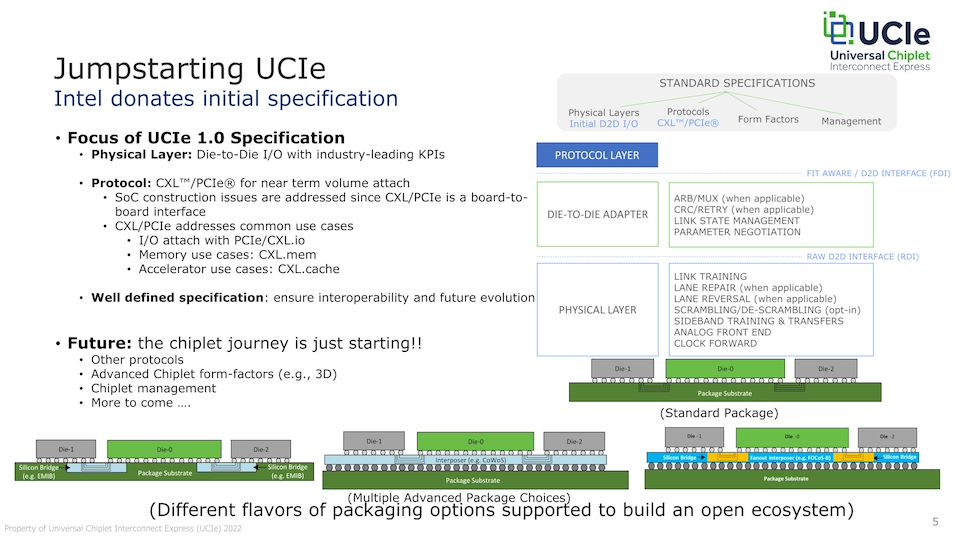

Hittills har alla aktörer som på något vis nyttjat tekniken gjort det med egna proprietära gränssnitt och kommunikationsbussar. Det här ska det bli ändring på med Universal Chiplet Interconnect Express (UCI Express). Det handlar kort och gott om en gemensam kommunikationsbuss som möjliggör för att kunna kombinera chiplets från olika aktörer. Bakom standarden står tunga namn som AMD, ARM, Google, Meta, Microsoft, Qualcomm, Samsung, TSMC och i sammanhanget framförallt Intel, som donerat specifikationen den nya standarden.

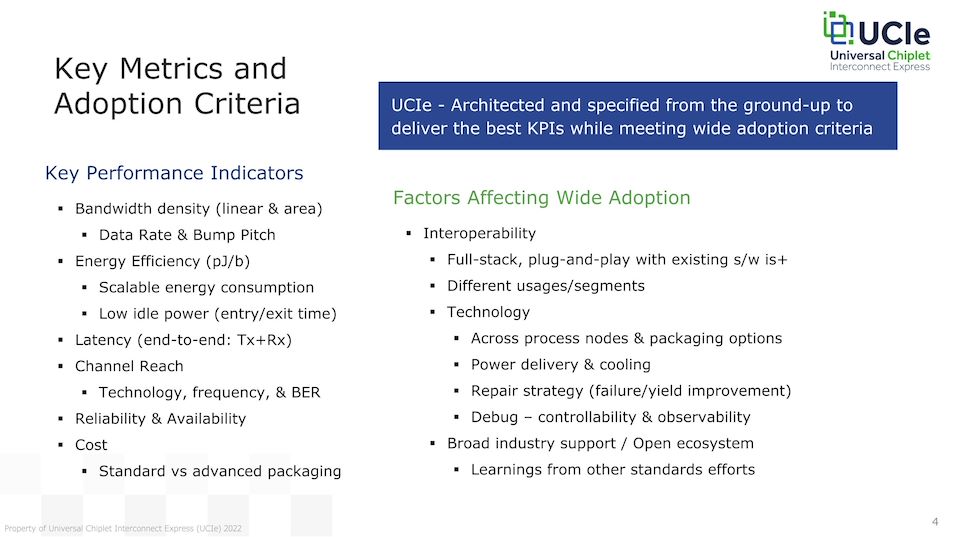

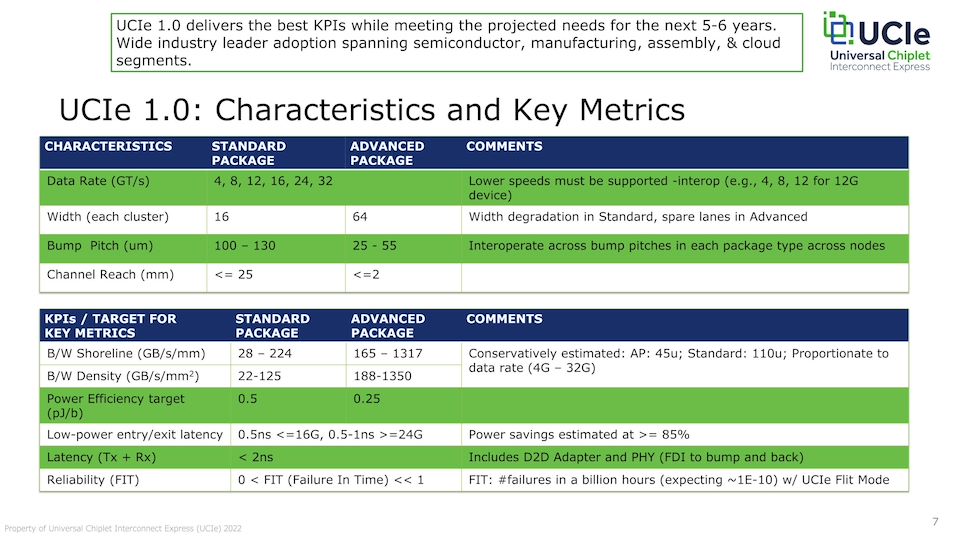

Som UCI Express beskrivs är syftet att fylla samma funktion för flera kretsar på ett substrat, chiplets, som PCI Express gör för instickskort. UCI Express ska även stävja chiplet-designers stora nackdel, nämligen att det jämfört med en monolitisk krets kostar sett till prestanda och energieffektivitet att skyffla data mellan olika kretsar. Det här är dock något som ofrånkomligt aldrig kommer gå att lösa helt.

Den nya standarden har beteckningen version 1.0 och teknikjättarna bakom gör tydligt att UCI Express 1.0 bara är början. De kommer med andra ord att vidareutveckla standarden med syfte att skapa ett ekosystem, där de och många fler på ett relativt enkelt vis ska kunna ”mixa och matcha” kretsar från olika aktörer.