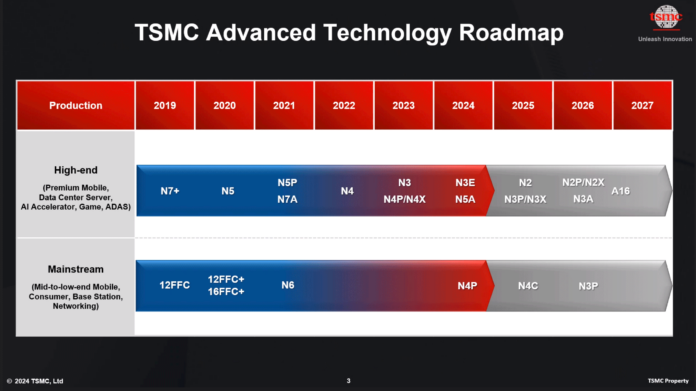

Världens största halvledartillverkare, taiwanesiska TSMC, utannonserade under sitt 2024 North America Symposium att steget efter N2 eller 2 nanometer blir A16 – 1,6 nanometer. Bolaget har länge varit tyst om framtiden efter 2 nanometer, som väntas gå i produktion under andra halvan av 2025, men nu står det klart att en ny process avlöser den redan efterföljande år.

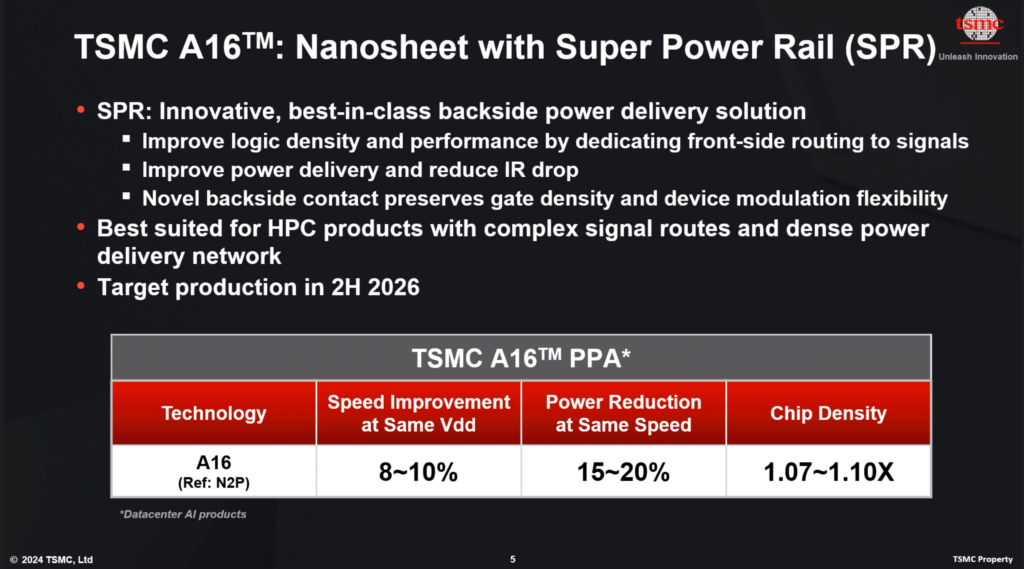

Nytt för A16 blir vad TSMC kallar Super Power Rail eller Backside Power Delivery (BSPD). Det hela innebär att TSMC blir sist i sällskapet med Intel och Samsung att införa tekniken, där Intel introducerar det redan i år med sin 2-nanometersprocess 20A. Samsung var först med transistorer av typen GAAFET med 3 nanometer och väntas till sin 2-nanometersprocess också införa BSPD år 2025.

Det hela innebär att TSMC ser ut att bli sist ut på marknaden med att kombinera de två teknikerna. Bolaget kommer introducera GAAFET, nanosheet på TSMC-lingo med 2025 års 2 nanometer (N2), och alltså först till 2026 med A16 introducera BSPD. Det hela avskräcker dock inte bolaget, som utlovar 8–16 procent högre frekvenser vid samma effektuttag, 15–20 procent lägre strömförbrukning vid samma frekvenser och upp till 1,1 gånger högre transistordensitet för datacenterkretsar som tillverkas på A16 jämfört med N2P.

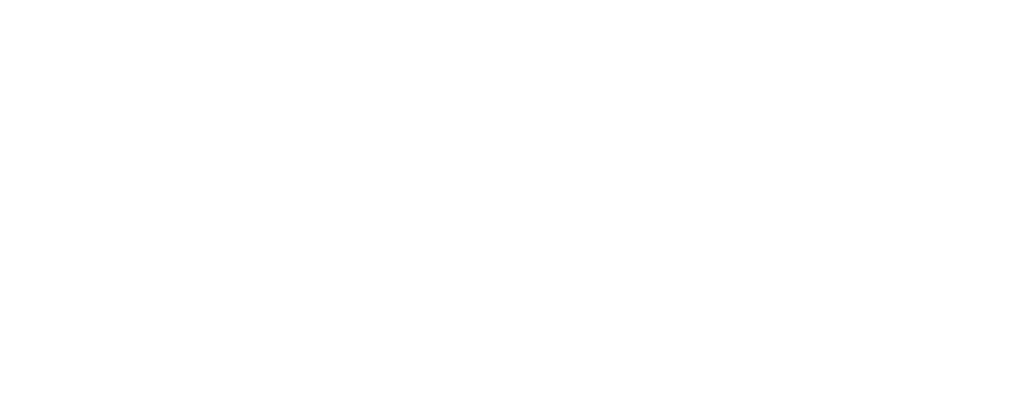

Även andra nyheter presenterades av bolaget under eventet, däribland en vidareutveckling av 4-nanometersprocessen N4P vid namn N4C. N4C positioneras som en billigare teknik än N4P som ska kräva minimala förändringar i designskedet och kosta 8,5 procent mindre än en kiselskiva N4P. Produktionsstart sker under 2025 och TSMC utlovar bättre yield än med N4P – det senare är normalt en paradgren för just den taiwanesiska kontraktstillverkaren.

Den avancerade paketeringstekniken Chip-on-Wafer-on-Substrate (CoWoS), bäst känt som paketeringstekniken Nvidia brukar för att para alla sina AI-beräkningskretsar med minne av HBM-typ, får en ny kusin år 2027. Det handlar om en uppdatering av Integrated Fan-Out-processen (System-on-Wafer, SoW) som kommer dra nytta av CoWoS-teknik och kommer medföra möjligheter att integrera SoIC (System on Integrated Chips), HBM och ”andra komponenter” direkt på kiselskivor vid produktion.

TSMC har likt Samsung en SoW-process i produktion, som i dagsläget är begränsad till endast logik utan extra tillbehör.