Efter lanseringen av ChatGPT november 2022 har marknaden för artificiell intelligens (AI) och maskininlärning (ML) växt explosionsartat. Med krav på mer beräkningskraft ökar pressen på tillverkarna att kunna producera tillräckligt med chip för att mätta marknaden, vilket i det här fallet gäller främst kontraktstillverkaren TSMC.

Under Semicon 2023 berättade TSMC:s styrelseordförande, Mark Liu, att det kommer ta runt 18 månader att komma tillrätta med bristen på AI-chip. Med andra ord skulle detta innebära att den begränsade utbudet biter sig kvar till 2025, men han tillägger samtidigt att en lättnad kan bli aktuell till slutet av 2024. Oavsett vilket är således bristen på bland annat Nvidias populära beräkningskort H100 och A100 här för att stanna i åtminstone ett år.

It’s not the shortage of AI chips. It’s the shortage of our COWOS [advanced chip packaging] capacity. […] Currently, we can’t fulfill 100% of our customers’ needs, but we try to support about 80%. We think this is a temporary phenomenon. After our expansion of [advanced chip packaging capacity], it should be alleviated in one and a half years.

– Mark Liu, styrelseordförande på TSMC

Att det råder brist på AI-kretsar kommersiellt är ett faktum, men under en tillställning på Semicon passade Liu på att gå in på ytterligare detaljer. Bolaget har inga problem att tillverka AI-kretsen som utför de faktiska beräkningarna, utan det handlar om kapacitet för tillverkning av Chip-on-Wafer-on-Substrate (CoWoS). Det är CoWoS som används för att sammanställa de mest avancerad AI-chipen som används kommersiellt idag.

TSMC gick nyligen ut med planer om att bygga en facilitet för 2,9 miljarder USD i Miaoli, Taiwan, som ska öka den viktiga CoWoS-produktionen. Då bolaget idag inte kan möta 100 procent av kundernas efterfrågan menar Liu att de försöker stötta dem ”till runt 80 procent”. Om detta innebär att TSMC gör en solidariskt rättvis fördelning mellan Nvidia, AMD och många fler framgår inte. Rapporter talar dock om att Nvidia ska ha köpt 40 procent av TSMC:s totala CoWoS-kapacitet för 2024.

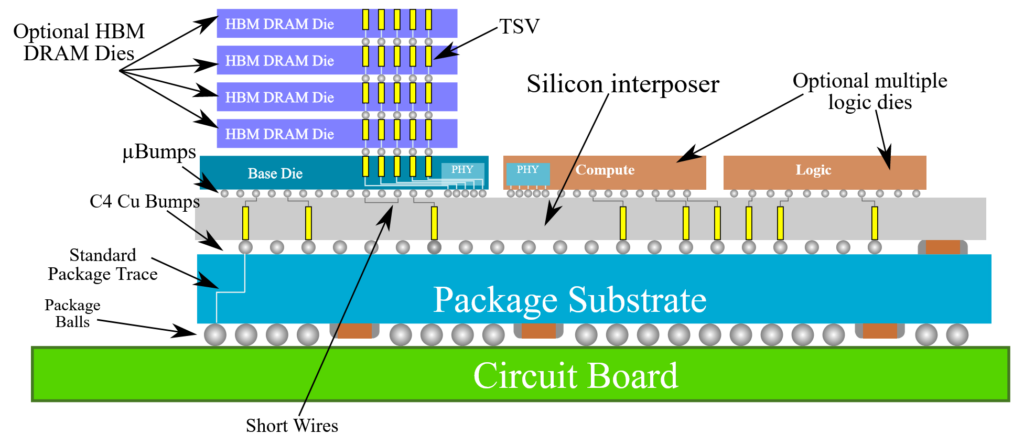

Paketeringstekniken CoWoS handlar om hur flera kretsar sätts samman för att utgöra en färdig produkt. I centrum är en bit kisel (W), en active interposer eller mellanlager om man så vill, och på denna placeras huvudkretsarna (C). Den vanligaste konstruktionen för sagda chip är en eller flera beräkningskretsar i mitten, vilka omgärdas av grafikminne av HBM-typ för att ge bandbredd om flertalet gigabyte per sekund. När denna process väl är avklarad placeras det färdiga paketet på ett substrat (S).

En traditionell design för beräkningskretsar, vilka i många fall är synonyma med grafikkretsar, är att en monolitisk design placeras direkt på ett substrat. Därefter ansluts kretsens minnesbuss till grafikminne av GDDR-typ över ledningsbanor på ett kretskort. Fördelen med detta är framförallt lägre produktionskostnad, vilket lämpar sig för exempelvis grafikkort konsumentled, medan CoWoS tillsammans med HBM erbjuder flerfaldigt mer bandbredd och betydligt högre energieffektivitet per skickad bit data.

Möjligheten att på ett energieffektivt sätt sammanfoga flera kretsar är en fördel med CoWoS som kommer bli allt viktigare längre fram, och då inte enbart för AI, datacenter och dylika applikationer. I takt med att krympningen av transistorer stannar av blir det oundvikligt att producera större kretsar. Problemet då ligger i den teoretiska gränsen för hur stor monolitisk krets som är möjlig att tillverka. Med de litografiska verktyg som används ligger gränsen på cirka 26 x 33 millimeter (858 mm²) och designer större än 800 mm² är något Nvidia sedan många år tillbaka producerat hos TSMC. Med CoWoS är det möjligt att sammanfoga kretsar på uppemot totalt 2 500 mm² och TSMC är i full färd med att utveckla CoWoS på upp till 5 000 mm².

Tidigare i sommar rapporterades att TSMC hade en tillverkningskapacitet för CoWoS om cirka 8 000 kiselskivor per månad. Detta hoppas de kunna skruva upp till 11 000 innan årsskiftet, för att mot slutet av 2024 nå en kapacitet om 14 500–16 500 kiselskivor per månad. Det har talats om att bolagets mål är att öka produktionstakten med hela 150 procent, vilket beroende på när ifrån man börjar räkna innebär från 20 000 kiselskivor per månad och uppåt år 2025.