Sedan Intel gick ut med sin ambitiösa plan om att introducera fem tillverkningstekniker på fyra år har fokus legat på PowerVia – Intel-språk för Backside Power Delivery (BSPD). Branschkollegan tillika konkurrenten TSMC som inte vill vara sämre har också talat öppet om BSPD, medan Samsung lyst med sin frånvaro vad gäller planer för tekniken.

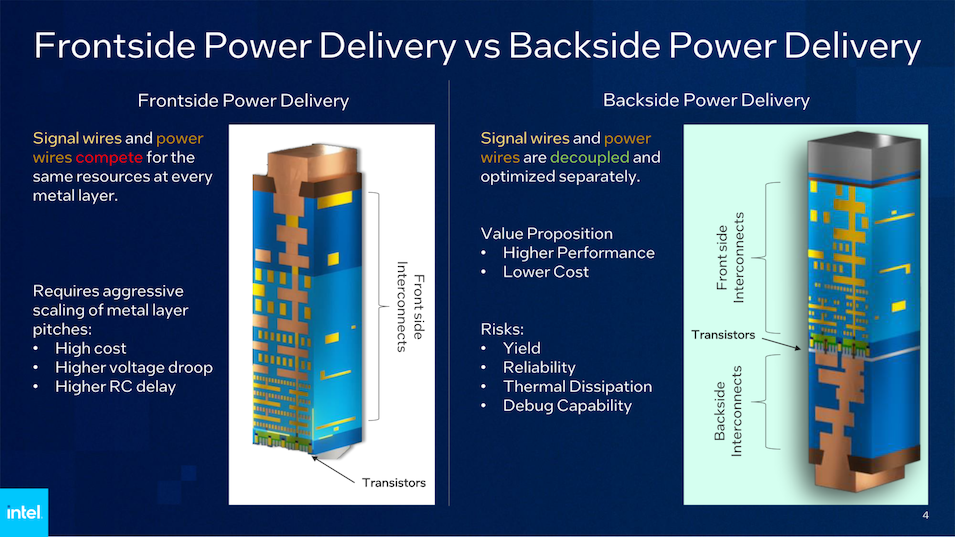

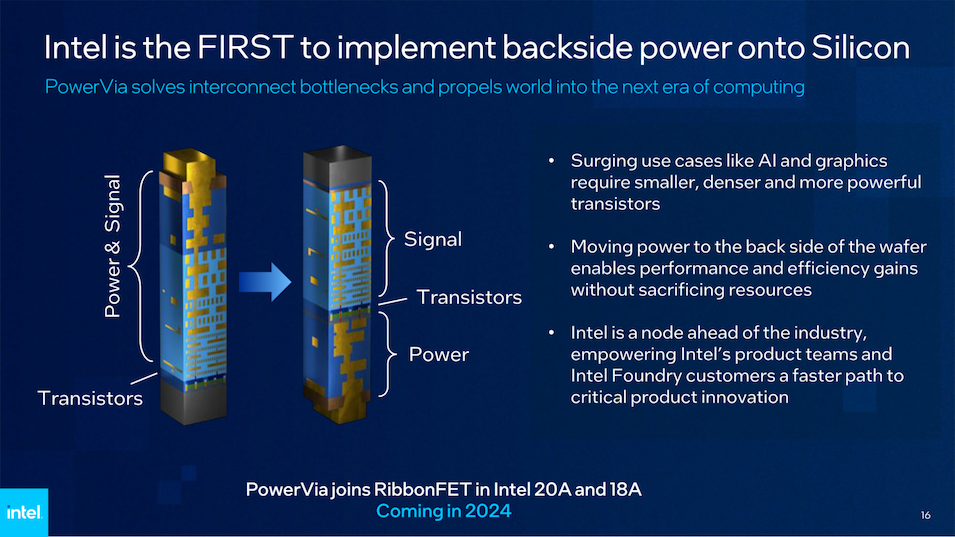

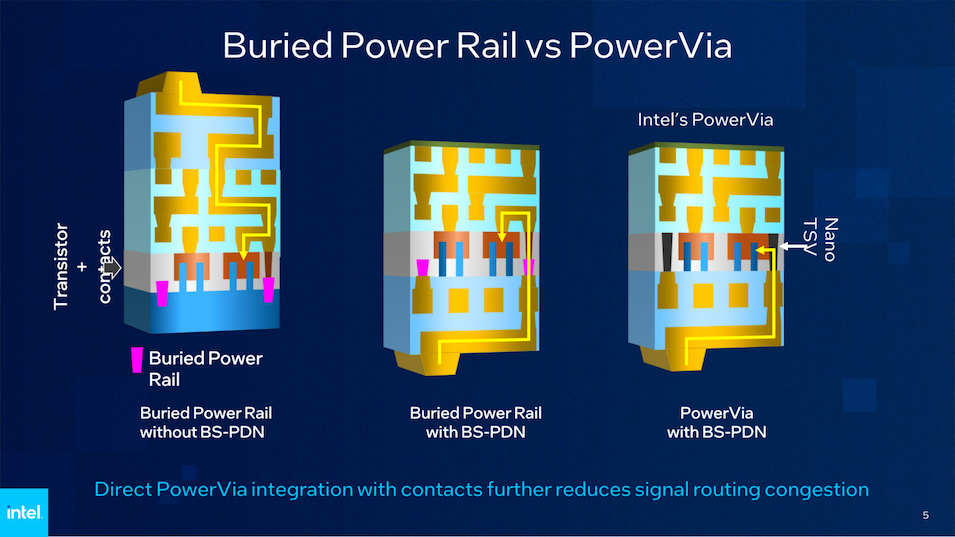

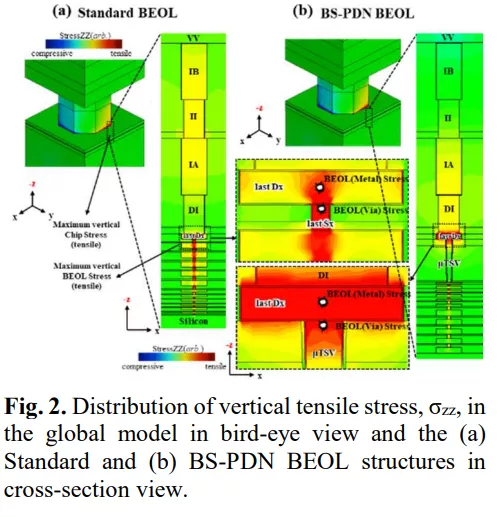

Nu rapporterar sydkoreanska The Elec om Samsungs ingång med BSPD, något som presenterades under VLSI Symposium i juni. Traditionellt delar strömförsörjning och transistorsignaler utrymme på kiselskivans ovansida, något som blivit ett allt större problem när vi rört oss mot mindre geometrier (det som i marknadsföring är nanometer). Förutom att ledningarna för båda delar konkurrerar om allt mindre utrymme ökar resistans, kapacitans och spänningsfall. Alla dessa problemområden ska mildras med BSPD.

När Samsung talar om fördelarna med BSPD är det i form av en icke-specificerad teknik, där kretsens area med tekniken minskade med 14,8 procent. Elektronikjätten nämner även specifikt två olika ARM-kretsar med en areaminskning om 10 och 19 procent. Rent konkret ger detta Samsung och potentiella kunder två alternativ; att addera fler transistorer till samma area som om BSPD inte används eller att tillverka en mindre, dyrare krets.

Vidare menar Samsung att längden på ledningarna kortas med 9,2 procent, vilket tillsammans med att göra dessa tjockare sänker resistansen. På så vis blir det möjligt att mata transistorerna med högre spänning och uppnå högre prestanda. Förbättringen på den senare fronten uppges vara 3,6 procent högre maximal klockfrekvens (Fmax).

Som ett företag med ambitioner om att ligga i spjutspetsen är det ingen överraskning att Samsung likt Intel och TSMC talar om BSPD, men utfästelser om när tekniken introduceras lyser med sin frånvaro. Intel har för avsikt att redan under 2024 års första hälft gå in i storskalig produktion med Intel 20A, 2 nanometer, som introducerar såväl PowerVia som RibbonFET. Det senare är Intel-lingo för Gate-All-Around Field Effect Transistor (GAAFET), som Samsung introducerade redan 2022 med sin 3-nanometersteknik.

TSMC å sin sida har ännu inte delgett några detaljer om sin BSPD-modell, men har yppat så mycket som att tekniken introduceras med andra generationens 2 nanometer. Då TSMC lanserar sin 2-nanometersteknik först 2025, med produkter sannolikt först under 2026, är en kvalificerad gissning att 2 nanometer med BSPD äntrar scen ett år senare.

Vad gäller Samsungs introduktion av BSPD finns egentligen två huvudkandidater. Under 2025 avser bolaget lansera sin 2-nanometersteknik, som antingen från start eller med en senare variant likt TSMC får BSPD. Ett annat alternativ är att Samsung planerar att introducera tekniken till 2027-års spjutspetsteknik 1,4 nanometer.