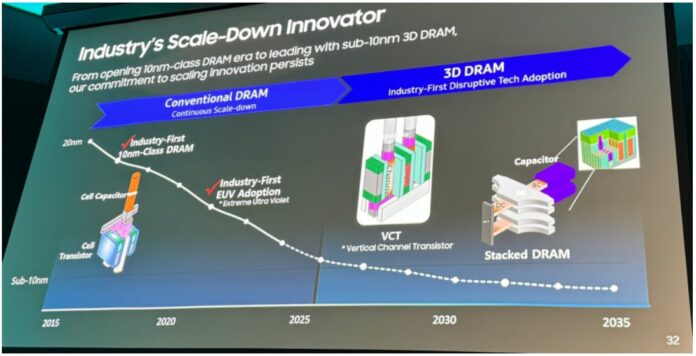

Sydkoreanska Samsung har bitvis kommit på efterkälken på minnesmarknaden, men ämnar i närtid att hårdsatsa på att komma ikapp landsmännen SK Hynix gällande HBM – och på längre sikt med 3D DRAM. Tanken är att Samsung till år 2030 ska ha kommersiell tillverkning av 3D-staplat DRAM, med mellanlandningar på transistorer av VCT-typ och krympningar av minneskapslarna så snart som år 2025 dessförinnan, rapporterar Zdnet Korea.

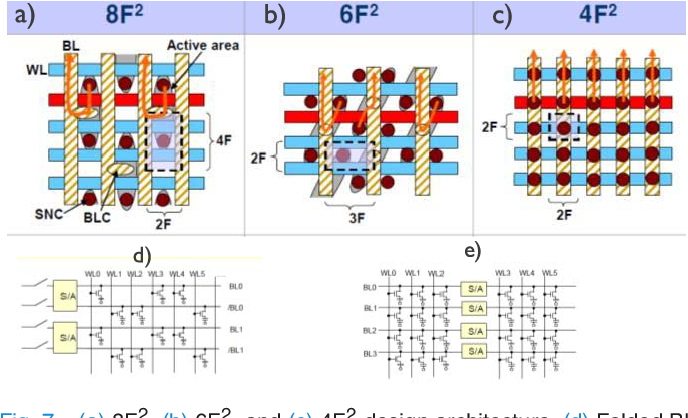

Samsung kungjorde sina planer under 2024 års IEEE IMW (International Memory Workshop), där Samsungs Lee Si-woo talade om bolagets forskningsframsteg med VCT (vertical channel transistor) och 3D DRAM. Framförallt är vägen till formfaktorn 4F Square VCT DRAM utstakad hos Samsung, vilket både krymper den fysiska storleken på en DRAM-krets med cirka 30 procent jämfört med dagens 6F Square-kretsar och lägger grund för möjligheten att effektivt stapla DRAM på ett sätt liknande moderna NAND-kretsar.

Med kommersialiserad produktion av 4F-celler och transistorer av VCT-typ ämnar Samsung att år 2030 uppnå produktion av 3D DRAM, där uppemot 16 lager per krets kan vara en startpunkt. Inga andra minnestillverkare har till dags dato ännu publikt vädrat tankar om att producera DRAM av 3D-typ – men ett av få bolag som publikt demonstrerat tekniken på just 4F-celler är kinesiska CXMT, dit Samsung-ingenjörer sålt affärshemligheter.

Industrial developments such as hyperscaler AI and on-demand AI require a lot of memory processing ability. On the other hand, the microprocessing technology of existing DRAM is limited […] New innovations are expected to occur in the structure of cells

– Lee Si-woo, Samsung

Lee sätter också ord på den relativa avsaknaden av utveckling på DRAM-marknaden, där minne av HBM-typ stulit showen i AI-beräkningskortens tidevarv. För konventionellt DRAM väntar han sig att framstegen kommer ske på cellnivå, där vertikala transistorer och stapling står på schemat och kan hjälpa DDR-minne skala i densitet på samma sätt som lagringsminne i NAND-format. Inom just NAND återtog Samsung nyligen taktpinnen med lanseringen av nionde generationens kretsar med 290 lager.

Nästa anhalt för Samsung på vägen mot 3D DRAM är testproduktion av transistorerna av VCT-typ, vilket inleds år 2025. Enligt Tom’s Hardware väntar sig utrustningsleverantören Tokyo Electron inte att VCT rullas ut i kommersiella produkter förrän år 2027.