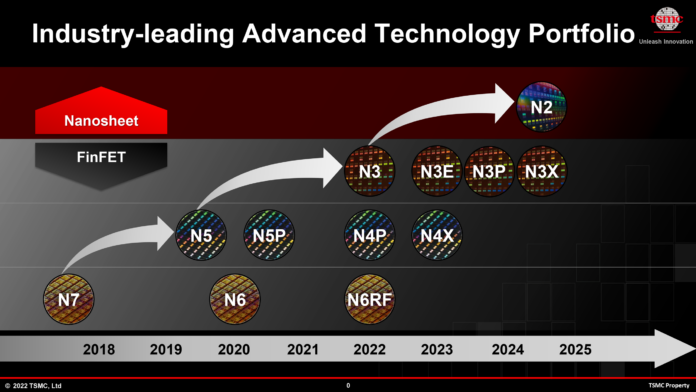

Att tillverkning av halvledare blir allt mer komplicerat och energikrävande i takt med att transistorer packas tätare är ingen nyhet. En av många anledningar att senaste generationens tillverkningsprocesser är kostsammare är bland annat övergången till EUV-litografi, där tillverkning ned till 5 nanometer klarade sig på äldre DUV-teknik.

Tillverkning av kretsar på 3 nanometer och mindre kräver med andra ord ny utrustning, som endast tillverkas av nederländska ASML – och för att strö salt i såren krävs även fler processteg, vilket leder till längre tillverkningstid och en ökad energikostnad. Denna energikostnad är att lägga till de 200 miljoner euro maskinerna har som styckpris.

Resultatet är att varje tillverkad 300 millimeter stor kiselskiva, wafer, med kretsar är rekorddyr. När Digitimes summerar kostnaderna når en wafer med 3-nanometerskretsar 20 000 USD, dubbelt så mycket som en skiva försedd med kretsar om 7 nanometer. Även 5 nanometer, processen där AMD och Nvidia låter tillverka sina senaste processorer och grafikkretsar, representerar ett 60-procentigt prispremium från just 7 nanometer.

Även Apple, traditionellt bolaget som är först ut att använda TSMC:s senaste tillverkningsprocesser, står i dagsläget kvar med produkter tillverkade på N4, andra generationens 5-nanometersprocess från den taiwanesiska kontraktstillverkaren. Med systemprocessorn A17, som väntas i kommande Apple-produkter, tas klivet till 3 nanometer, och således ökar också systemprocessorns pris med 25 procent.

På annat håll rapporteras också Samsung att än en gång ha sjösatt en tillverkningsprocess med bedrövlig yield, andel fungerande kretsar per wafer, med sin 3 nanometer GAAFET. Den sydkoreanska tillverkaren har något av en historia att kommersialisera processer för att påvisa tillverkningstekniska försprång gentemot TSMC och att svälja kostnaden i jakt på marknadsandelar.

Digitimes rapporterade under april, innan lanseringen av Samsungs 3-nanometersprocess, att yield endast uppgick till 10–20 procent – att ställa mot 90–95 procent i en mogen process i massproduktion. Detta menar taiwanesiska Commercial Times gäller än, då Samsung uppges ha tagit hjälp av det amerikanska bolaget Silicon Frontline Technology för att förbättra situationen.

Samsung väntas fasa in andra generationens 3 nanometer (3GAP) för att avlösa dagens 3GAE, där E som av en händelse står för ”early”. Att Samsung väljer att ta in extern hjälp antyder dock att utvecklingen mot 3GAP inte gått smärtfritt och att bolagets marginaler kan stå på spel.