När Intel 2024 introducerar tillverkningstekniken Intel 20A (2 nanometer) tillkommer samtidigt två stora nyheter – Gate-All-Around Field Effect Transistor (GAAFET) och Backside Power Delivery (BSPD). På Intel-språk är detta RibbonFET respektive PowerVIA, där det senare är någonting Intel i egenskap av kontraktstillverkare hoppas ska ge en fördel mot TSMC och Samsung.

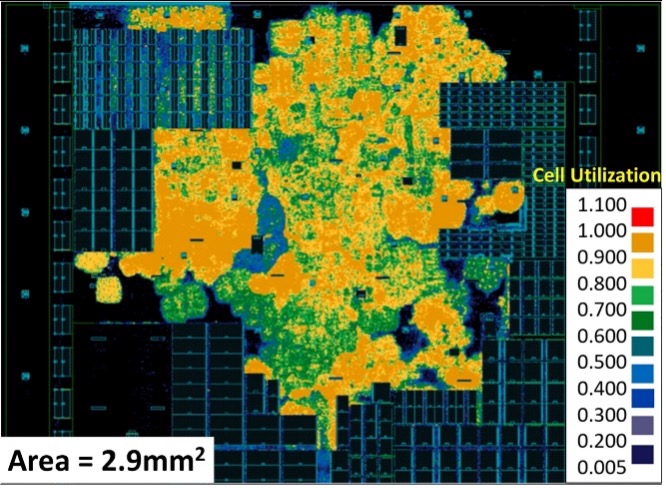

PowerVia enabled standard cell utilization of greater than 90 percent in large areas of the core while showing greater than 5 percent frequency benefit in silicon due reduced IR drop. Successful Post silicon debug is demonstrated with slightly higher but acceptable throughput times. The thermal characteristics of the PowerVia testchip is inline with higher power densities expected from logic scaling.

– IEEE Symposium on VLSI Technology and Circuits

Den 11–16 juni pågår 2023 Symposium on VLSI Technology and Circuits och där ska Intel den 13 juni (PDF) för första gången demonstrera PowerVIA. Intressant nog ska detta inte göras på tillverkningstekniken Intel 20A utan på nästkommande Intel 4, som introduceras senare under året, och med en enklare processor med en E-Core-arkitektur. Vare sig Intel 4 med PowerVIA eller processorn i fråga kommer att kommersialiseras, utan de handlar om uteslutande experimentella tillämpningar av vad som komma skall med Intel 20A och Intel 18A.

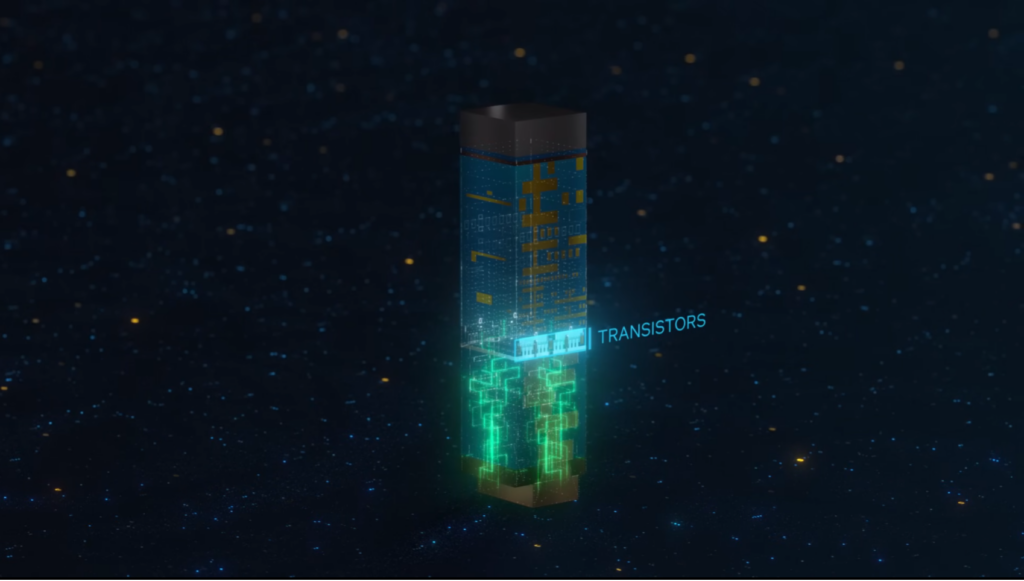

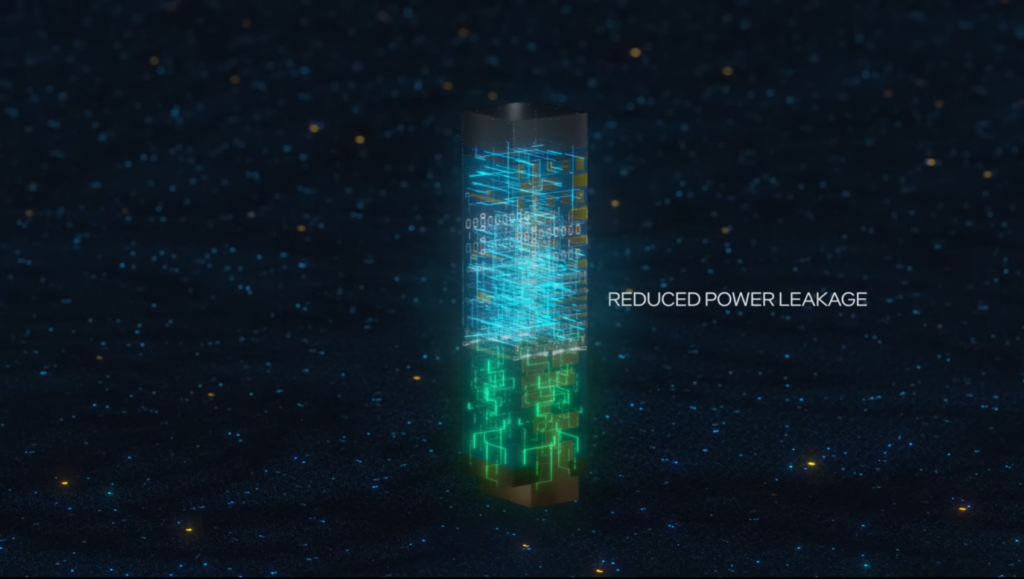

Konceptet Backside Power Delivery eller PowerVIA syftar till att flytta strömförsörjningen till baksidan av kiselskivan, där den inte behöver konkurrera om plats med transistorernas utsignaler. De tydligaste fördelarna med tekniken är att det sänker resistans och kapacitans, mildrar spänningsfall och möjliggör för mer energieffektiva designer med högre klockfrekvens. Samtidigt blir det lättare att dra ledningsbanor mellan transistorerna, vilket i sin tur möjliggör för ökad transistordensitet med en given tillverkningsteknik.

Att tekniken är framtiden råder det inga tvivel om och att den introduceras i närtid har att göra med att ovannämnda är växande problem med varje ny tillverkningsteknik där högre densitet tillkommer. Nackdelen är i vanlig ordning ökad komplexitet vid tillverkning och därigenom kostnad, något som till viss del kan tänkas kompenseras av att komplexiteten att dra ledningsbanor i designstadiet minskar och att densiteten ökar.

Om allt går enligt plan ska Intel 20A som blir först ut med både RibbonFET och PowerVIA gå in i produktion tidigt 2024. Denna teknik är i första hand ämnad Intel själva och målet är att ha produkter ute på marknaden till slutet av året. Under 2024 års andra hälft ska bolaget introducera Intel 18A, vilken är den teknik som är ämnad potentiella kunder. Förutsatt att Intel levererar i tid kommer de föra TSMC, vilka introducerar sin motsvarande 2-nanometersteknik med GAAFET, som de kallar Nanosheet, och Backside Power Delivery.