I samband med IEEE International Electron Devices Meeting (IEDM) levererar Intel en rad nyheter inom tillverkning av halvledare, eller rättare sagt en inblick i vad som komma skall. Tonvikt på vad världens största processortillverkare presenterar ligger på tekniker som ligger 5–10 år bort i tiden och som ska bana väg mot kretsar med så mycket som en biljon – 1 000 miljarder – transistorer till 2030.

Intels utfästelse är minst sagt ambitiös sett till halvledarvärlden idag. Världens idag mest avancerade chip med monolitisk design är beräkningskretsen H100 från Nvidia med 80 miljarder transistorer och en area om 814 mm², vilket är nära den så kallade reticle limit som råder. Detta är gränsen för hur stor krets som med dagens litografiska utrustning är möjlig att tillverka.

Till följd av att grafikkretsar är svåra att tillverka framställs Nvidias krets på TSMC:s idag näst mest avancerade teknik 4 nanometer, en förfinad variant på 2020 års 5 nanometer. Fram till 2030 väntas bolaget ha tagit steget ned till 2 nanometer och sannolikt även dess efterföljare, som väntas leverera knappa dubbleringar i transistortäthet, optimistiskt räknat. Med enkel matematik landar vi, inklusive ett stopp på 3 nanometer dessförinnan, långt ifrån en biljon transistorer på ett chip.

För att möjliggöra målet om en biljon transistorer 2030 ska Intel använda sig av chiplets där flera chip sammanfogas för att skapa en komplett produkt, ”ett” chip om man så vill. Den stora fördelen med att använda chiplets är kostnadseffektivitet. Medan logiska transistorer skalar relativt väl med mer avancerade tillverkningstekniker är detsamma inte fallet med exempelvis analoga transistorer och SRAM-cacheminne. Tanken är då att de senare kan tillverkas på en äldre teknik och sedan sammanfogas med kretsen tillverkas på en nyare. En minst lika viktig aspekt är att ju större en monolitisk krets är, desto mer benägen är den att få defekter vid tillverkning.

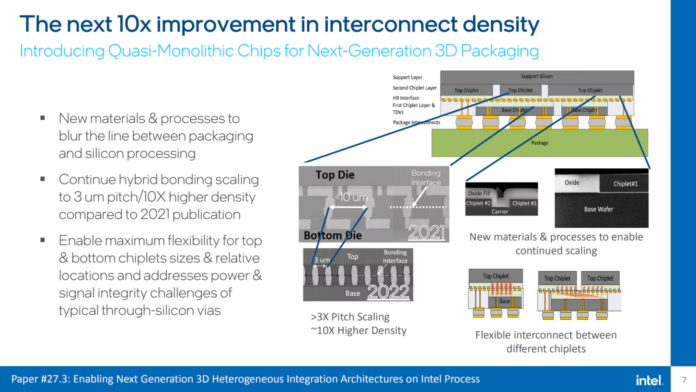

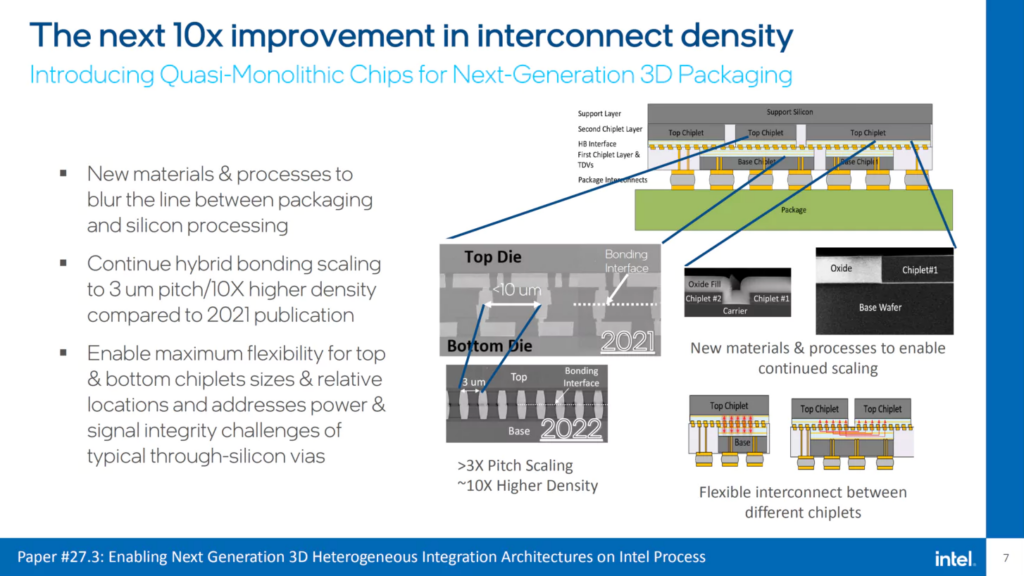

Tekniken med dess ekonomiska fördelar har även sin beskärda del nackdelar. När olika kretsar till skillnad från en monolitisk ska kommunicera med varandra påverkar det prestandan i form av ökade latenser. När data ska skickas mellan kretsar tillkommer även ett påslag i energiförbrukning, räknat i joules per bit. Dessa är ofrånkomliga nackdelar som industrin arbetar på att minimera genom att ta fram mer avancerade interconnects.

Kretsar kan placeras antingen på bredden eller höjden och fokus för Intel är det senare, vilket i praktiken innebär att slutprodukten inte blir orimligt stor areamässigt. När kretsar placeras ovanpå varandra minskar även avståndet, vilket i sig medför minskade påslag gällande latenser och energiförbrukning. För att ytterligare förbättra sagda aspekter har Intel på endast ett år lyckats tiodubbla densiteten på de anslutningspunkter som sammanfogar varje chiplet.

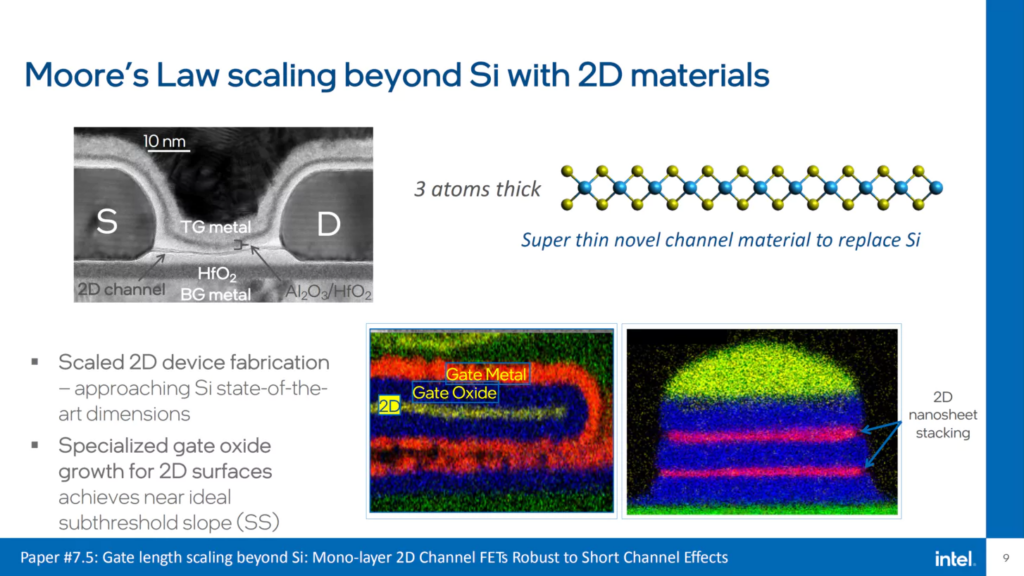

Användningen av chiplets är endast en av många tekniker för att nå Intels biljonmål. En annan är fortsatt krympning av transistorer, vilket blir allt svårare och dyrare att åstadkomma för varje ny generation. Ett annat problem är som det ofta uttrycks att vi håller på att ”få slut på atomer”, vilket låter lika roligt som det faktiskt är sant.

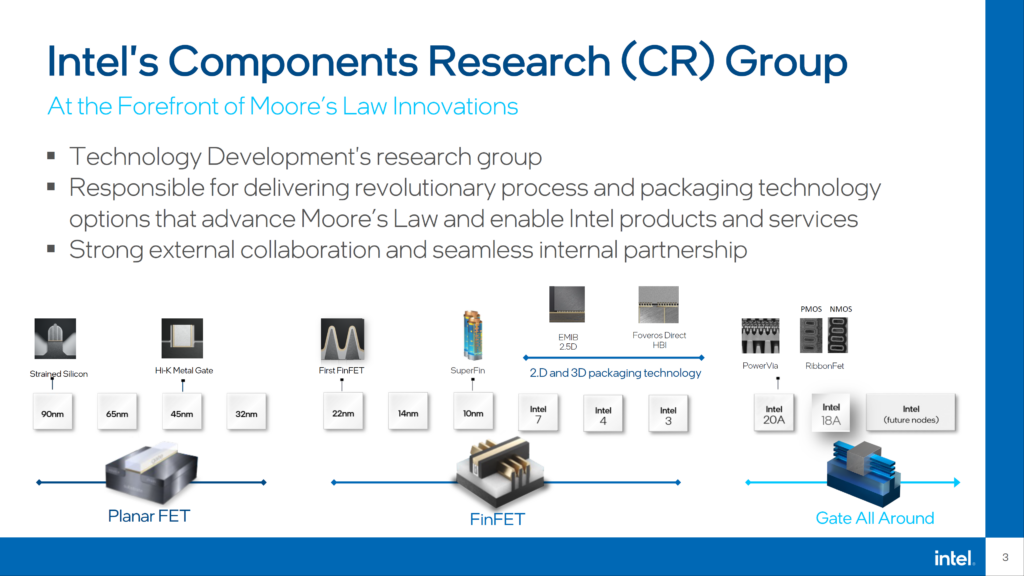

Samsung lanserade under året sin 3-nanometersteknik med Gate-All-Around Field-Effect Transistor (GAAFET), där själva kanalen lyfts och omgärdas av en transistorgrind. Detta för att ge ännu bättre kontroll, lägre elektronläckage och möjligheten att driva transistorer med lägre drivspänning. Ökat läckage är ett växande problem vid krympning av transistorer.

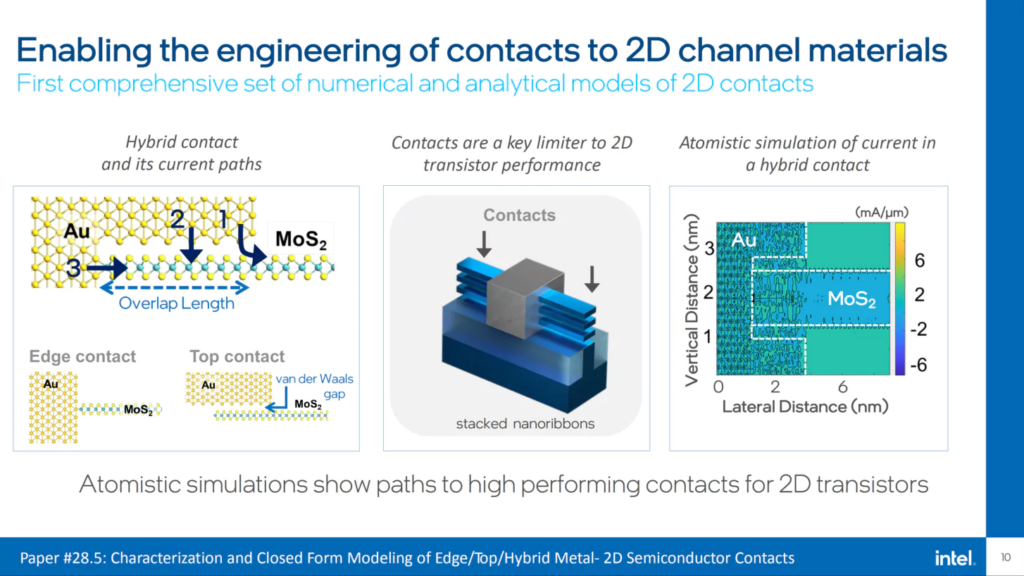

I samband med tekniken 20A (2 nanometer) lanserar Intel sin variant av GAAFET kallad RibbonFET, som ersätter dagens FinFET-transistorer. Framtida avancemang kommer kräva ytterligare en ny typ av transistor och här blickar industrin som helhet mot vad som kallas 2D-atomkanaler, som ersätter kisel. Här ser Intel framför sig kanaler som är blott tre atomer tjocka och en kandidat för detta är materialet molybdendisulfid, MoS².

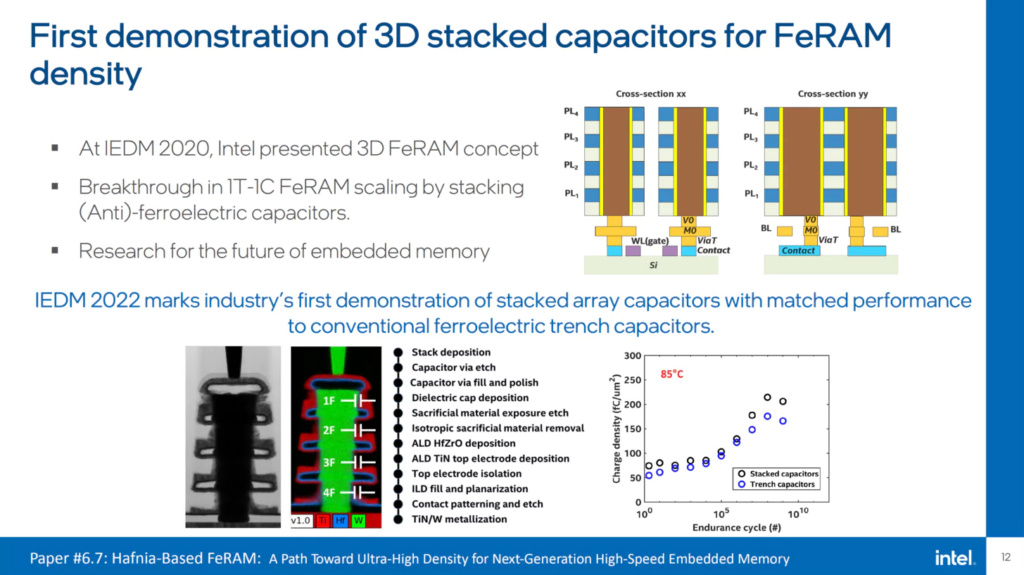

Den tredje tekniken Intel lyfter fram för att nå målet om en biljon transistorer per kvasi-monolitisk krets är stapling av transistorer. Det här känns närmast igen från NAND som är den minnestyp som används för lagring i alltifrån USB-minnen till SSD-enheter och annan konsumentelektronik, som exempelvis telefoner. Dagens NAND-minnen staplar så mycket som 238 lager minnesceller ovanpå varandra. Tanken är att använda en liknande minnesteknik även för bland annat processorer, där cacheminne av typen static random-access memory (SRAM) bygger på bredden och tar upp allt mer kretsyta i förhållande till själva beräkningsenheterna.

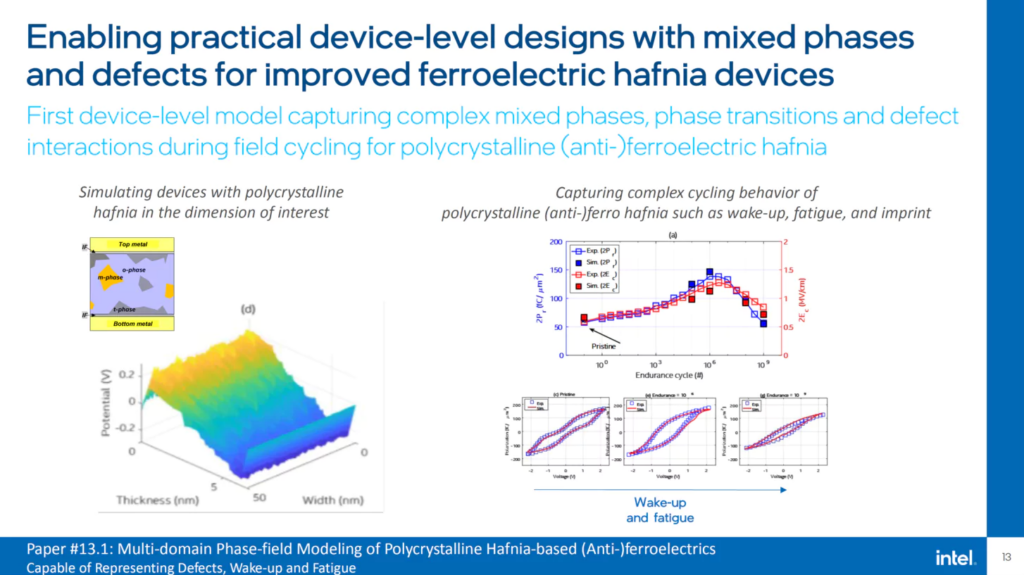

En kandidat för detta är ferroelectric random access memory (FeRAM). Det är en minnesteknik som länge funnits på marknaden och tros ha stor potential, men som industrin inte investerat nämnvärt i. De kretsar som säljs tillverkas på ålderdomliga tekniker som 350 och 130 nanometer och de största har en kapacitet om blott 16 Mb (2 MB). Minnestekniken ses främst som ett möjligt alternativ till NAND och dynamic random-access memory (DRAM) som används för primärminne, men kan även används som ett komplementärt cacheminne vid sidan om traditionellt SRAM.

Under IEDM 2020 presenterade Intel konceptet med 3D FeRAM, som namnet anger är staplade minnesceller av typen FeRAM, och nu två år senare menar Intel att de lyckats tillverka en sådan pjäs med fyra lager. Därtill hävdar Intel att deras 3D FeRAM har prestandaegenskaper i paritet med FeRAM som byggs planärt eller ”på bredden”. En annan fördel med FeRAM är att den i likhet med NAND är icke-volatil och kan hålla spänningen även när strömmen slås av, något som inte är möjligt med SRAM och DRAM som båda är volatila.

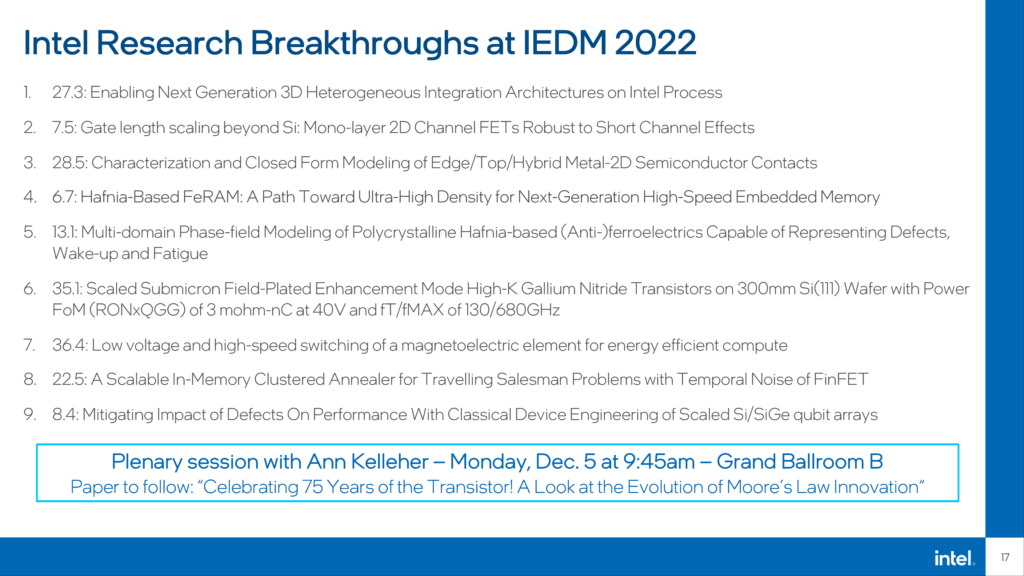

Det här är endast några av många möjliga vägar framåt för Intel att fortsätta leverera nya chip med högre prestanda till lägre strömförbrukning, samtidigt som de håller kostnaderna i schack. Nyheterna som presenteras här är en kort överblick av vad som komma skall under IEDM 2022, där Intel den 5 december ska släppa nio mer omfattande dokument på deras forskning. Semi14 får anledning att återkomma till dessa.